本刊翻譯| 李玲珊

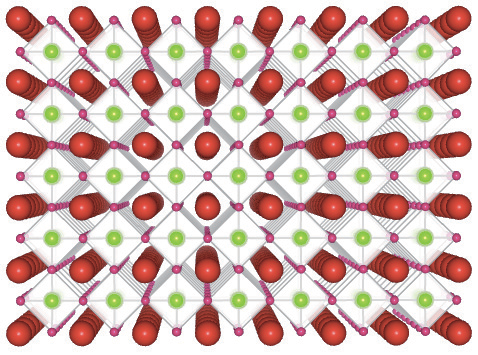

鐵電材料的原子結(jié)構(gòu)展現(xiàn)了所謂的“負(fù)電流容量”效果。如果這一結(jié)構(gòu)能成功應(yīng)用于晶體管的構(gòu)成,將會(huì)大幅度減少計(jì)算機(jī)處理器和其他由晶體管構(gòu)成的設(shè)備的用電量。

--Suraj S. Cheema

在今天出版的《自然材料》雜志中, 有一篇文章稱首次直接觀測(cè)到了“負(fù)電容” 現(xiàn)象。上述現(xiàn)象長(zhǎng)期存在人們的假設(shè)中, 但卻又難以捉摸。上述文章描述一種電荷與外加在某種鐵電材料上的電壓所發(fā)生的獨(dú)特反應(yīng),且上述反應(yīng)為大幅度降低晶體管和含晶體管設(shè)備的用電量帶來了曙光。

電容指是某種材料存儲(chǔ)電荷的能力。事實(shí)上,在幾乎所有的電子器件中都能找到常規(guī)的電容器。當(dāng)向這些電容器施加一定的電壓時(shí),它們就開始存儲(chǔ)電荷。但是, 上述新發(fā)現(xiàn)卻呈現(xiàn)出一種異常反應(yīng):當(dāng)增大外加電壓時(shí),所存儲(chǔ)的電荷反而減少。“負(fù)電容”現(xiàn)象也因此得名。

雜志的首席作者Asif Khan 稱:“如果將這一特性整合到晶體管中,其耗電量將至少降低一個(gè)數(shù)量級(jí)甚至更多。”這將會(huì)帶來更加持久的手機(jī)電池,各種類型的低能耗計(jì)算機(jī)。更重要的是,微處理器自誕生之日起就定義了其后的數(shù)字革命,而這一成果可以將處理器更小、更快的發(fā)展趨勢(shì)延長(zhǎng)幾十年。

如果沒有類似的重大突破,由于運(yùn)行在納米尺度下的晶體管的實(shí)際需求的限制, 處理器微型化和多功能化的趨勢(shì)就會(huì)受到威脅。盡管微型開關(guān)能夠做得更小,但在開和關(guān)操作中可節(jié)省的電量也就那么多。上述限制由“波爾茲曼電子分布”所決定, 也常為稱為“波爾茲曼限制”。因?yàn)檫@些晶體管必須消耗一定量的電量,當(dāng)超小型晶體管被太過緊密地排列在一起時(shí),它們所散發(fā)出的熱量則無法及時(shí)發(fā)散出去,從而導(dǎo)致晶體管自身受損。

大約再過十年,工程師將窮盡辦法也無法將更多計(jì)算能力整合到更小的空間內(nèi), 這無論是對(duì)于設(shè)備制造商、傳感器開發(fā)商還是沉迷于更小、更強(qiáng)大設(shè)備的公眾來說都是噩夢(mèng)。

上述研究在加州大學(xué)伯克利分校完成, 其具體負(fù)責(zé)人是社會(huì)前沿信息技術(shù)研究中心(CITRIS,Center For Information Technology Research In The Interest Of Society)研究員、電氣工程與計(jì)算機(jī)科學(xué)學(xué)院副教授Sayeef Salahuddin。由Sayeef Salahuddin 教授牽頭, 其創(chuàng)造性地提出了一種可能克服“波爾茲曼限制”的途徑。上述目的的實(shí)現(xiàn)要依靠某些材料通過自身的特性來存儲(chǔ)能量,并利用上述能量來放大輸入電壓。上述方法在實(shí)際操作中有可能“騙過”晶體管,使其認(rèn)為已經(jīng)接收到了運(yùn)行所需的最小電壓。如果上述目的能夠?qū)崿F(xiàn),其結(jié)果就是:用于將晶體管打開或關(guān)閉的能量得以減少。而開關(guān)晶體管是所有計(jì)算機(jī)處理核心中最常用的操作。

用于實(shí)現(xiàn)“負(fù)電容”的材料屬于鐵電晶體類,關(guān)于其最早的記載可以追溯至上世紀(jì)40 年代。在內(nèi)存應(yīng)用和商業(yè)存儲(chǔ)技術(shù)方面,這些材料都經(jīng)歷了長(zhǎng)期的研究過程。此外,鐵電材料也經(jīng)常用于頻率控制電路許多微機(jī)電系統(tǒng)應(yīng)用中。但是,將上述材料應(yīng)用于節(jié)能晶體管中還是由Salahuddin 于2008 年首次提出,就在他以助理教授的身份加入伯克利之前。

在過去的6 年里,作為Salahuddin 在伯克利帶的第一批畢業(yè)生之一,Khan 利用脈沖激光制備出了許多種鐵電材料并設(shè)計(jì)和改進(jìn)了多種獨(dú)創(chuàng)性方法來測(cè)試它們的負(fù)電容性能。

除了用于改變晶體管工作方式,“負(fù)電容”也可能被用于開發(fā)高密度記憶存儲(chǔ)設(shè)備、超級(jí)電容器、無線圈振蕩器和共鳴器以及從環(huán)境中獲得能量。

“作為減少存儲(chǔ)一比特信息所消耗焦耳量的策略之一,鐵電材料的”負(fù)電容“ 特性被充分利用了起來。”論文的另一作者,加州大學(xué)伯克利分校材料學(xué)、工程學(xué)和物理學(xué)教授Ramamoorthy Ramesh 說道。Ramesh 花了幾十年時(shí)間用于研究鐵電材料和設(shè)備結(jié)構(gòu)的特性,以達(dá)到操控它們的目的。他的前期開創(chuàng)性工作是整個(gè)團(tuán)隊(duì)的發(fā)現(xiàn)打下了堅(jiān)實(shí)的基礎(chǔ)。

“我們已經(jīng)啟動(dòng)了一個(gè)名為”attojoule-per-bit“的項(xiàng)目,努力使運(yùn)行一比特信息的總能耗減少至1 attojoule(10-18)。要實(shí)現(xiàn)每比特信息能耗量那么少的目標(biāo),我們需要充分利用所有可能的途徑。鐵電材料的”負(fù)電容“將會(huì)是非常重要的一條途徑。”

這項(xiàng)工作由于CITRIS 的馬維爾納米制造實(shí)驗(yàn)室(Marvell Nanofabrication Laboratory)的支持而得以進(jìn)行。上述實(shí)驗(yàn)室位于加州大學(xué)伯克利分校內(nèi),其特別注重于鼓勵(lì)新材料與新工序的研發(fā)與利用。作為世界上同類型實(shí)驗(yàn)中最頂尖的之一, 該實(shí)驗(yàn)室是許多劃時(shí)代技術(shù)的誕生地和發(fā)源地。這其中,三維鰭式場(chǎng)效應(yīng)晶體管(three-dimensional FinFET transistor)是其中典型的代表,其引導(dǎo)了打破常規(guī)晶體管限制的大潮流。“如今,所有的下一代微型處理器或計(jì)算機(jī)所使用的晶體管都是鰭式場(chǎng)效應(yīng)晶體管”馬維爾納米制造實(shí)驗(yàn)室主任吳銘教授說道。

“CITRIS 的馬維爾納米制造實(shí)驗(yàn)室擁有用于制備導(dǎo)體裝置和集成電路的最先進(jìn)設(shè)備。”吳教授說道。“但我們充分利用了這些設(shè)備和能力,并將它們應(yīng)用于一些最新的材料上。上述材料由于太過新穎,以至于工業(yè)制造實(shí)驗(yàn)室不會(huì)觸及到它們。在我們這里, 類似于”負(fù)電容“鐵電材料不僅會(huì)得到普遍歡迎,還會(huì)得到積極的鼓勵(lì)。”

“下一步我們將制備出真正利用到了上述新現(xiàn)象的晶體管。我們必須確保上述晶體管與硅制程是可兼容的、可制備的。此外, 我們還需確保在原則上已經(jīng)被證明可行的測(cè)試技術(shù)具備可實(shí)際操作性和可擴(kuò)展性。”

免責(zé)聲明:本網(wǎng)站所轉(zhuǎn)載的文字、圖片與視頻資料版權(quán)歸原創(chuàng)作者所有,如果涉及侵權(quán),請(qǐng)第一時(shí)間聯(lián)系本網(wǎng)刪除。

-

標(biāo)簽: 鐵電

相關(guān)文章

無相關(guān)信息

官方微信

《腐蝕與防護(hù)網(wǎng)電子期刊》征訂啟事

- 投稿聯(lián)系:編輯部

- 電話:010-62316606-806

- 郵箱:fsfhzy666@163.com

- 腐蝕與防護(hù)網(wǎng)官方QQ群:140808414

文章推薦

點(diǎn)擊排行

PPT新聞

“海洋金屬”——鈦合金在艦船的

點(diǎn)擊數(shù):8135

腐蝕與“海上絲綢之路”

點(diǎn)擊數(shù):6475